# **Sequential Circuit (Register)**

### Introduction: Registers

- An *n*-bit register has a group of *n* flip-flops and some logic gates and is capable of storing *n* bits of information.

- The flip-flops store the information while the gates control when and how new information is transferred into the register.

- Some functions of register:

- ✤ retrieve data from register

- store/load new data into register (serial or parallel)

- shift the data within register (left or right)

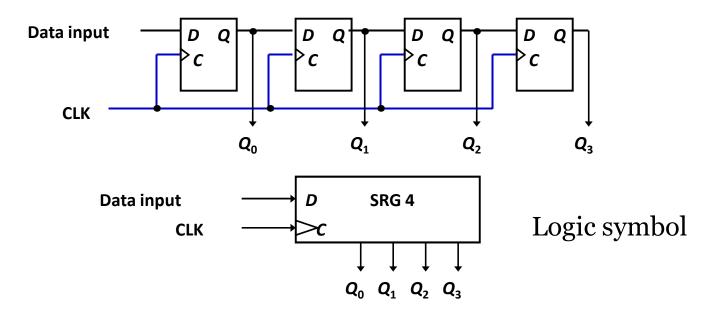

### Simple Registers

- No external gates.

- Example: A 4-bit register. A new 4-bit data is loaded every clock cycle.

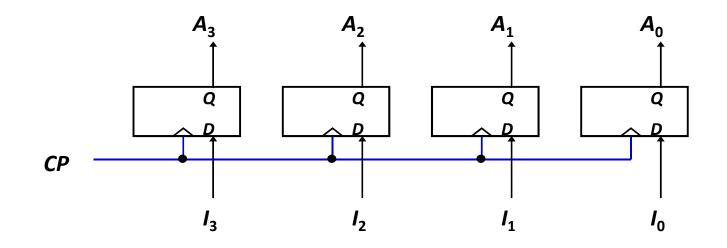

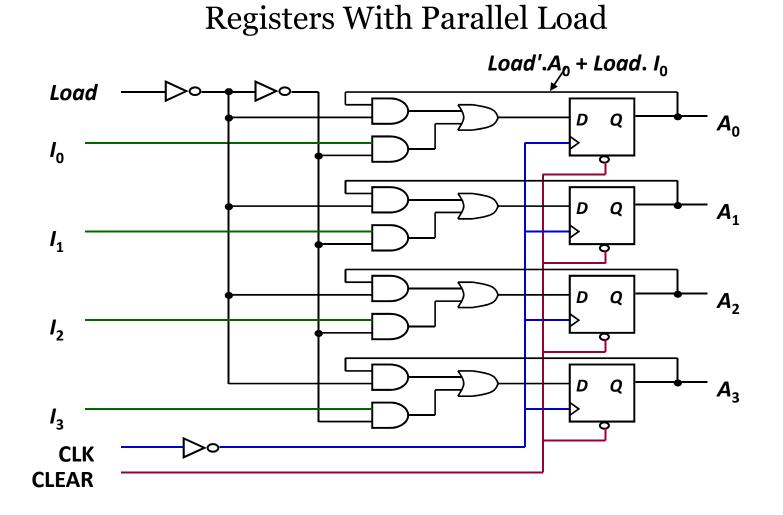

### **Registers With Parallel Load**

- Instead of loading the register at every clock pulse, we may want to control when to load.

- *Loading* a register: transfer new information into the register. Requires a *load* control input.

- *Parallel loading*: all bits are loaded simultaneously.

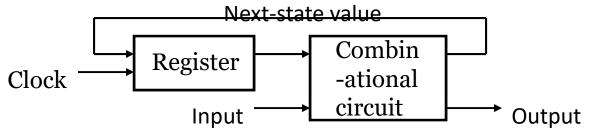

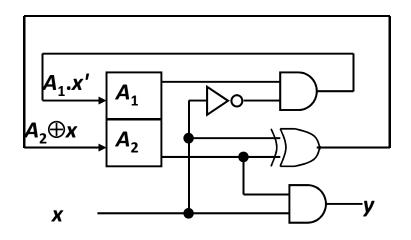

## **Using Registers to implement Sequential Circuits**

• A sequential circuit may consist of a *register* (memory) and a *combinational circuit*.

- The external inputs and present states of the register determine the next states of the register and the external outputs, through the combinational circuit.

- The combinational circuit may be implemented by any of the methods covered in *MSI components* and *Programmable Logic Devices*.

#### Cont...

• Example 1:  $A_1^+ = S m(4,6) = A_1 x'$   $A_2^+ = S m(1,2,5,6) = A_2 x' + A_2' x = A_2 \oplus x$  $y = S m(3,7) = A_2 x$

| Present<br>state      |                       | Input | Output      |             |   |

|-----------------------|-----------------------|-------|-------------|-------------|---|

| <b>A</b> <sub>1</sub> | <b>A</b> <sub>2</sub> | x     | $A_{1}^{+}$ | $A_{2}^{+}$ | у |

| 0                     | 0                     | 0     | 0           | 0           | 0 |

| 0                     | 0                     | 1     | 0           | 1           | 0 |

| 0                     | 1                     | 0     | 0           | 1           | 0 |

| 0                     | 1                     | 1     | 0           | 0           | 1 |

| 1                     | 0                     | 0     | 1           | 0           | 0 |

| 1                     | 0                     | 1     | 0           | 1           | 0 |

| 1                     | 1                     | 0     | 1           | 1           | 0 |

| 1                     | 1                     | 1     | 0           | 0           | 1 |

### Cont...

-

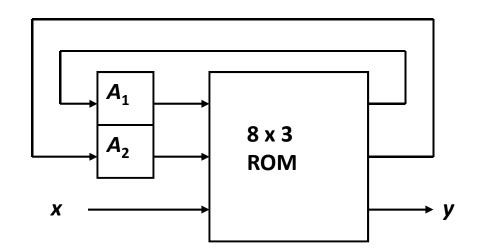

• Example 2: Repeat example 1, but use a ROM.

| Address |   |   | Outputs |   |   |  |

|---------|---|---|---------|---|---|--|

| _1      | 2 | 3 | 1       | 2 | 3 |  |

| 0       | 0 | 0 | 0       | 0 | 0 |  |

| 0       | 0 | 1 | 0       | 1 | 0 |  |

| 0       | 1 | 0 | 0       | 1 | 0 |  |

| 0       | 1 | 1 | 0       | 0 | 1 |  |

| 1       | 0 | 0 | 1       | 0 | 0 |  |

| 1       | 0 | 1 | 0       | 1 | 0 |  |

| 1       | 1 | 0 | 1       | 1 | 0 |  |

| 1       | 1 | 1 | 0       | 0 | 1 |  |

ROM truth table

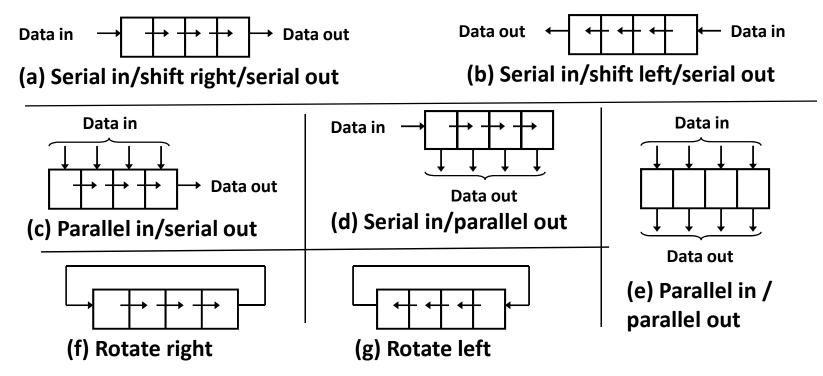

### **Shift Registers**

- Another function of a register, besides storage, is to provide for *data movements*.

- Each *stage* (flip-flop) in a shift register represents one bit of storage, and the shifting capability of a register permits the movement of data from stage to stage within the register, or into or out of the register upon application of clock pulses.

### Cont...

Basic data movement in shift registers (four bits are used for illustration).

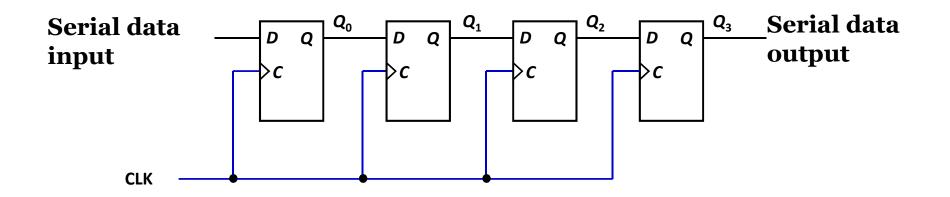

### Serial In/Serial Out Shift Registers

Accepts data serially – one bit at a time – and also produces output serially.

### Serial In/Serial Out Shift Registers

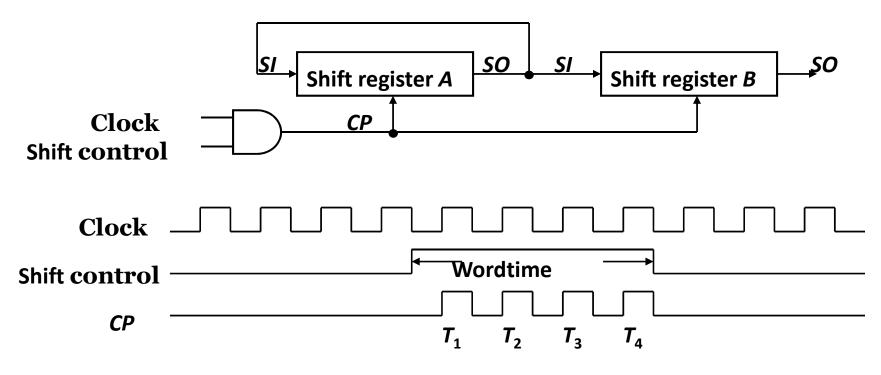

Application: Serial transfer of data from one register to another.

### **Serial In/Serial Out Shift Registers**

Serial-transfer example.

| Timing Pulse                | Shift register A |          |          | Shi            | Shift register B |          |          | Serial output of <b>B</b> |   |

|-----------------------------|------------------|----------|----------|----------------|------------------|----------|----------|---------------------------|---|

| Initial value               | <u> </u>         | 0        | 1、       | _1_            | 0                | 0、       | _ 1 、    | 0                         | 0 |

| After T <sub>1</sub>        | <b>1</b>         | <b>1</b> | <b>0</b> | <sup>¥</sup> 1 | 1                | <b>0</b> | <b>0</b> | <sup>™</sup> 1            | 1 |

| After T <sub>2</sub>        | 1                | 1        | 1        | 0              | 1                | 1        | 0        | 0                         | 0 |

| After $T_3$                 | 0                | 1        | 1        | 1              | 0                | 1        | 1        | 0                         | 0 |

| After <i>T</i> <sub>4</sub> | 1                | 0        | 1        | 1              | 1                | 0        | 1        | 1                         | 1 |

### Serial In/Parallel Out Shift Registers

- Accepts data serially.

- Outputs of all stages are available simultaneously.