# Sequential Circuit (Shift Register Counters)

### **Shift Register Counters**

- Shift register counter: a shift register with the serial output connected back to the serial input.

- They are classified as counters because they give a specified sequence of states.

- Two common types: the *Johnson counter* and the *Ring counter*.

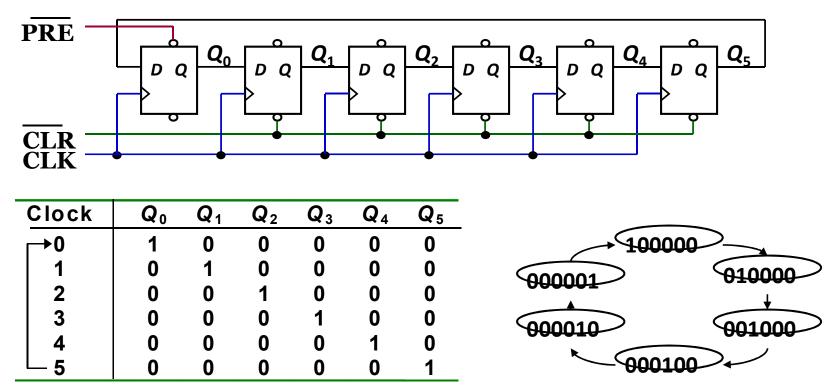

# **Ring Counters**

- One flip-flop (stage) for each state in the sequence.

- The output of the last stage is connected to the D input of the first stage.

- An *n*-bit ring counter cycles through *n* states.

- No decoding gates are required, as there is an output that corresponds to every state the counter is in.

#### **Ring Counters**

• Example: A 6-bit (MOD-6) ring counter.

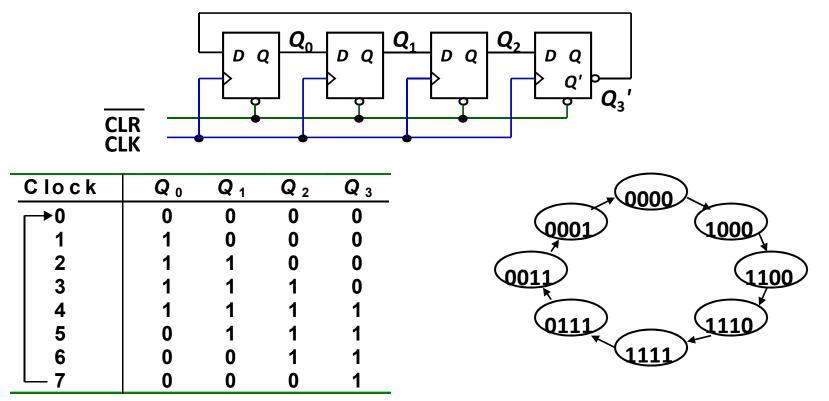

## **Johnson Counters**

- The complement of the output of the last stage is connected back to the D input of the first stage.

- Also called the *twisted-ring counter*.

- Require fewer flip-flops than ring counters but more flipflops than binary counters.

- An *n*-bit Johnson counter cycles through 2*n* states.

- Require more decoding circuitry than ring counter but less than binary counters.

#### Cont...

• Example: A 4-bit (MOD-8) Johnson counter.

#### Cont...

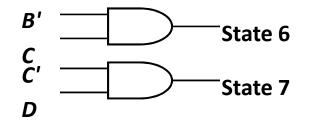

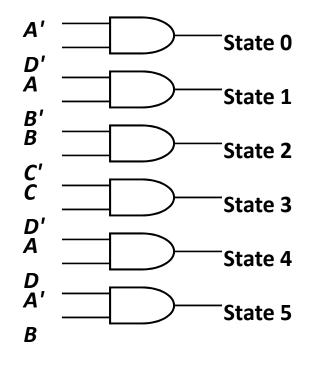

Decoding logic for a 4-bit Johnson counter.

| Clock |     | Α | В | С | D | Decoding |

|-------|-----|---|---|---|---|----------|

| ▶0    |     | 0 | 0 | 0 | 0 | A '.D '  |

|       | 1   | 1 | 0 | 0 | 0 | A.B'     |

|       | 2   | 1 | 1 | 0 | 0 | B.C'     |

|       | 3   | 1 | 1 | 1 | 0 | C.D'     |

|       | 4   | 1 | 1 | 1 | 1 | A.D      |

|       | 5   | 0 | 1 | 1 | 1 | A '.B    |

|       | 6   | 0 | 0 | 1 | 1 | В'.С     |

|       | - 7 | 0 | 0 | 0 | 1 | C '. D   |