## ALTERA CYCLONE PROCESSOR

The Cyclone device family offers the following features:

- 2,910 to 20,060 LEs, see Table 1–1

- Up to 294,912 RAM bits (36,864 bytes)

- Supports configuration through low-cost serial configuration device

- Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards

- Support for 66- and 33-MHz, 64- and 32-bit PCI standard

- High-speed (640 Mbps) LVDS I/O support

- Low-speed (311 Mbps) LVDS I/O support

- 311-Mbps RSDS I/O support

- Up to two PLLs per device provide clock multiplication and phase shifting

- Up to eight global clock lines with six clock resources available per logic array block (LAB) row

- Support for external memory, including DDR SDRAM (133 MHz), FCRAM, and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) cores, including Altera MegaCore functions and Altera Mega functions Partners

Program (AMPPSM) megafunctions.

# Cyclone II EP2C20 Device Block Diagram

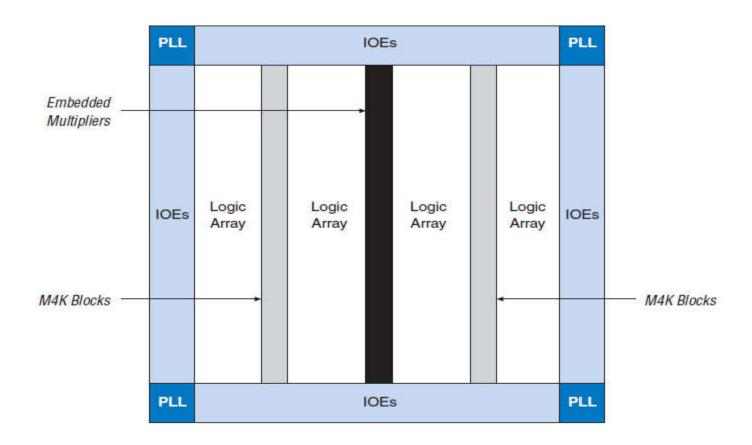

=> Cyclone® devices contain a two-dimensional row- and column-based architecture to implement custom logic. Column and row interconnects of varying speeds provide signal interconnects between LABs and embedded memory blocks.

# Cyclone II LE

### **LE Operating Modes**

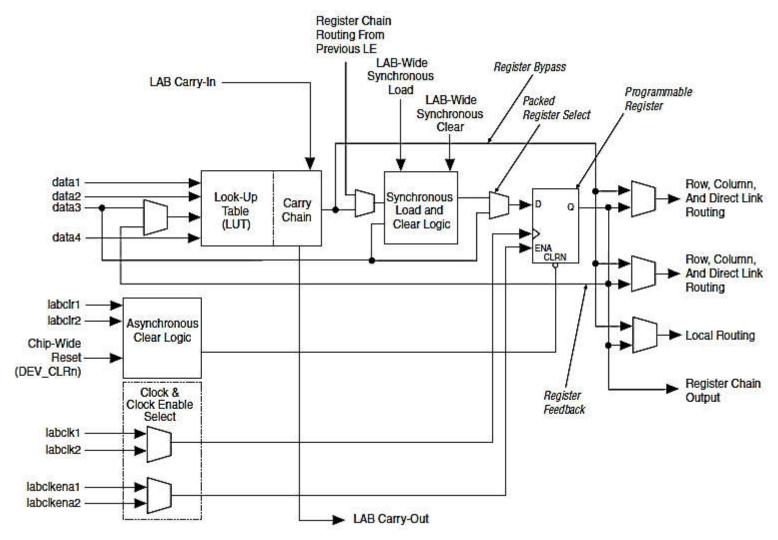

The Cyclone II LE operates in one of the following modes:

■ Normal mode

■ Arithmetic mode

#### **Normal Mode**

#### **Normal Mode**

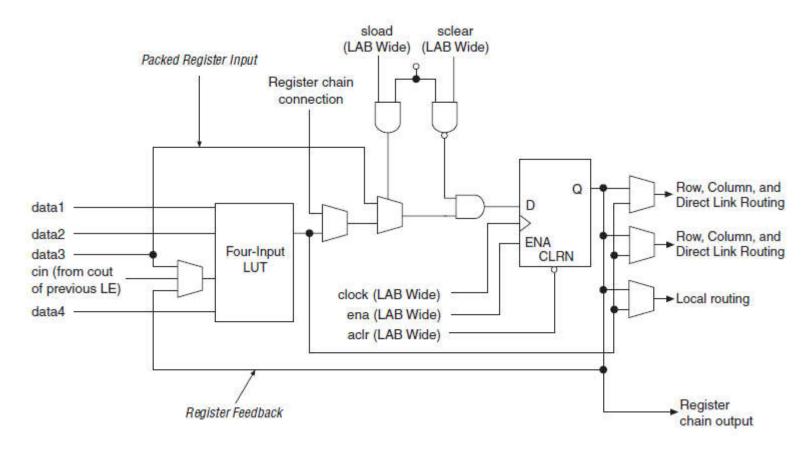

The normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT . The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

### **LE in Normal Mode**

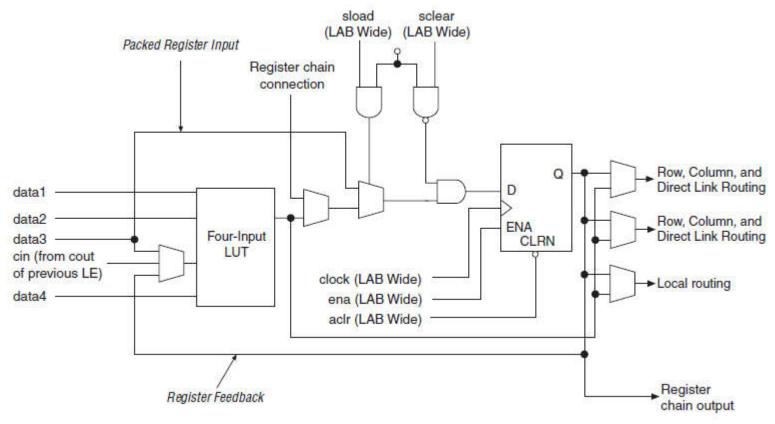

#### **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, counters, accumulators, and comparators. An LE in arithmetic mode implements a 2-bit full adder and basic carry chain (see Figure 2–4). LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output. Register feedback and register packing are supported when LEs are used in arithmetic mode.