# Partitioning and Floorpalnning

#### Partitioning

#### Centurion University

Shaping Live Composition of complex systems into smaller Subsystem

- Each subsystem can be designed independently

- Decomposition scheme has to minimize the interconnection between the systems

- Decomposition is carried out hierarchically until each subsystem is of manageable size.

#### Levels of Partitioning

Level Partitioning

System

**PCBs**

Chips

Subcircuits / Blocks

#### Circuit Representation

Centurion

UNIVERSITY

Stop of Lists ... State Communities...

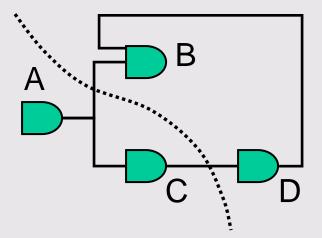

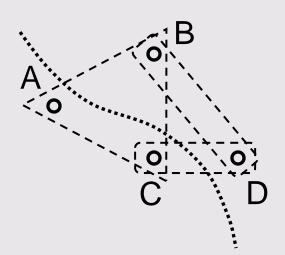

Gates: A, B, C, D

Nets: {A,B,C}, {B,D}, {C,D}

Hypergraph:

Vertices: A, B, C, D

Hyperedges: {A,B,C}, {B,D}, {C,D}

#### Partitioning Rule

Centurion University

Interconnection between the Partition is minimized.

Delay due to partitioning is minimized.

Number of terminals less than predetermined maximum value.

The area of each partition remains with in specific bounds.

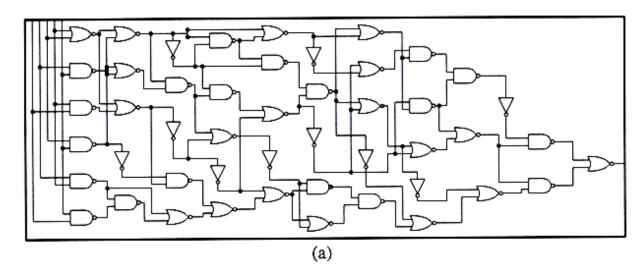

## Partitioning of a Circuit

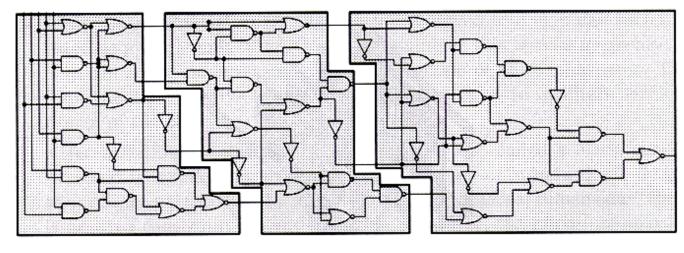

### What is Floorplanning?

Centurion University

Explored anning nothing but a plan a house Floorplanning.

Find approximate locations of a set of modules that need to placed on layout surface.

Available region typically considered rectangular, modules are also typically rectangular In shape but there can be exceptions(e.g-Lshape)

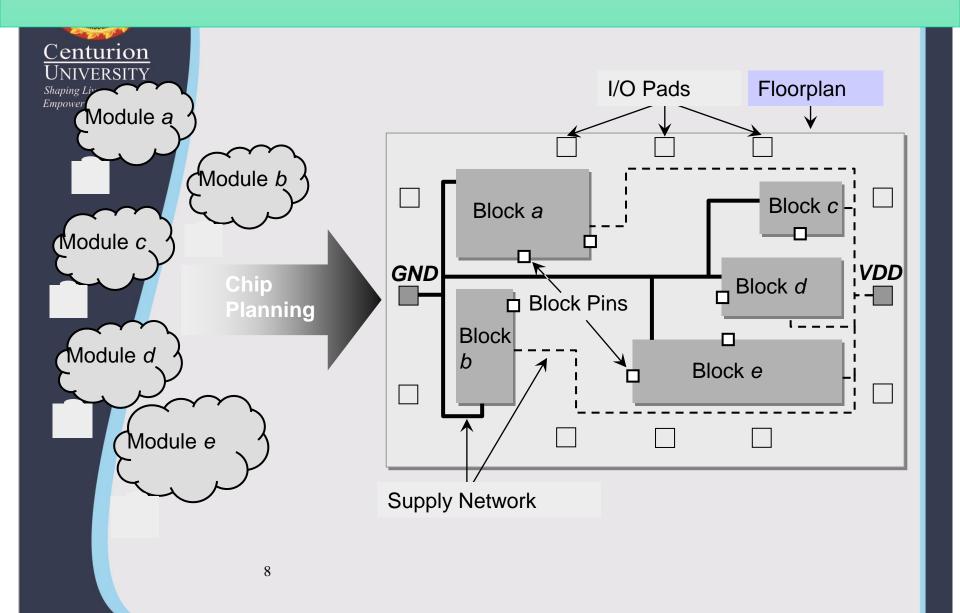

### Typical Floorplan

#### Floor plan Terminology

#### Floorplan Goals

Arrange the blocks on a chip

Place the Macros

Decide the location of the I/O pads

Decide the location and number of the power pads

Decide the type of power distribution

#### Floor Plan Inputs

University

Sharing Life the Sis Netlist

Physical Libraries

Logic Libraries

Timing constraints

Power requirement

Floor planning control parameters

#### Synthesis Netlist

simplest form, a netlist consists of a list of the electronic components in a circuit and a list of the nodes they are connected to.

It can be in the form of Verilog or VHDL.

This netlist is produced during logical, synthesis, which takes place prior to the physical design stage.

#### Physical Library

Reference libraries contains physical information of standard, macro and pad cells, which is necessary for placement and routing.

These libraries define placement file like height of placement rows, minimum width resolution, preferred routing direction pitch of routing tracks.

#### Logic Libraries

functionality information an each and every standard cells used in the design. It also provides timing information such as IP,ROM, RAM etc.

### Timing Constraints

and min insertion delay, no. of clock domains, clock start points (whether port level or internally generated)

#### Floor Planning Problem

shapes of the modules at the beginning of the design cycle to optimize the performance of the circuits:

- chip area

- > total wirelength

- delay of critical paths

- routability

- In floorplanning several alternatives for each block are considered

#### Floorplan Challenges

- > Congestion

- > Timing

- Power Network Design

- > Electro-Migration

- > IR Drop