# ELECTRONIC DEVICES AND CIRCUIT THEORY

#### TENTH EDITION

### Chapter 7: FET Biasing

## **Common FET Biasing Circuits**

#### **JFET Biasing Circuits**

- Fixed Bias

- Self-Bias

- Voltage-Divider Bias

### **D-Type MOSFET Biasing Circuits**

Self-BiasVoltage-Divider Bias

### **E-Type MOSFET Biasing Circuits**

Feedback ConfigurationVoltage-Divider Bias

### **Basic Current Relationships**

For all FETs:

$$I_G \cong 0A$$

$I_D = I_S$

For JFETS and D-Type MOSFETs:

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right)^{2}$$

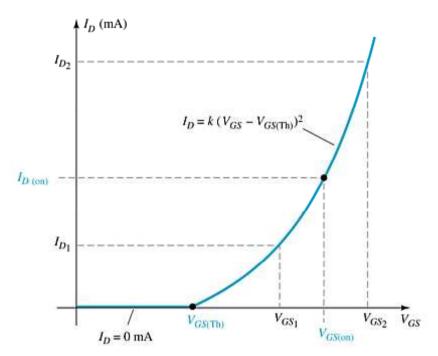

**For E-Type MOSFETs:**

$$\mathbf{I}_{\mathbf{D}} = \mathbf{k}(\mathbf{V}_{\mathbf{GS}} - \mathbf{V}_{\mathbf{T}})^2$$

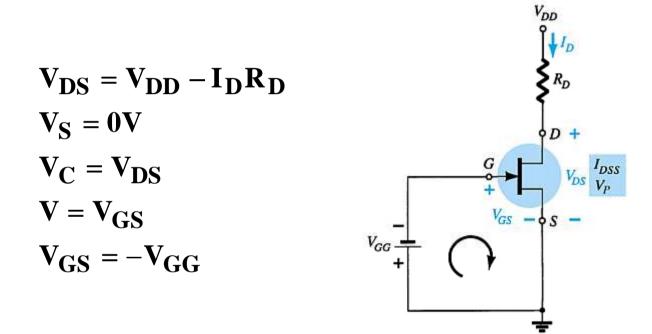

### **Fixed-Bias Configuration**

Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky

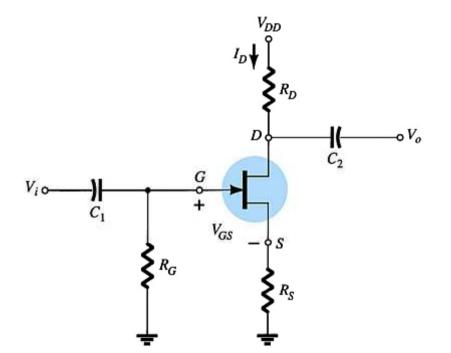

## **Self-Bias Configuration**

Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky

## **Self-Bias Calculations**

For the indicated loop,  $V_{GS} = -I_D R_S$ To solve this equation:

- Select an  $I_D < I_{DSS}$  and use the component value of  $R_S$  to calculate  $V_{GS}$

- Plot the point identified by I<sub>D</sub> and V<sub>GS</sub>. Draw a line from the origin of the axis to this point.

- Plot the transfer curve using  $I_{DSS}$  and  $V_P (V_P = V_{GSoff}$  in specification sheets) and a few points such as  $I_D = I_{DSS}/4$  and  $I_D = I_{DSS}/2$  etc.

The Q-point is located where the first line intersects the transfer curve. Use the value of  $I_D$  at the Q-point  $(I_{DQ})$  to solve for the other voltages:

$$\begin{split} \mathbf{V_{DS}} &= \mathbf{V_{DD}} - \mathbf{I_D}(\mathbf{R_S} + \mathbf{R_D}) \\ \mathbf{V_S} &= \mathbf{I_D}\mathbf{R_S} \\ \mathbf{V_D} &= \mathbf{V_{DS}} + \mathbf{V_S} = \mathbf{V_{DD}} - \mathbf{V_{RD}} \end{split}$$

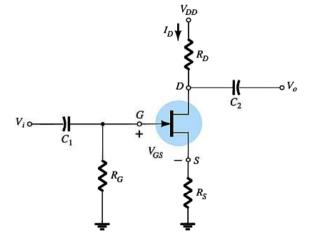

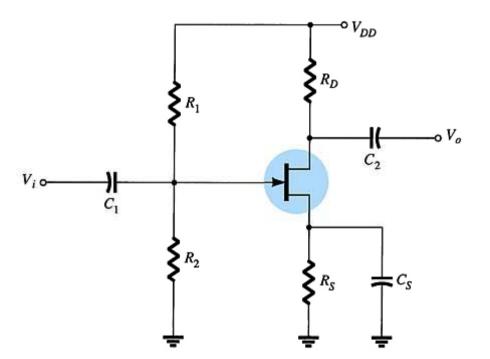

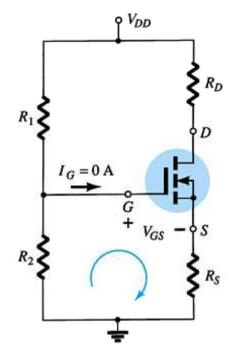

## **Voltage-Divider Bias**

$I_G = 0 A$

$I_{\rm D}$  responds to changes in  $V_{\rm GS}.$

## **Voltage-Divider Bias Calculations**

**V**<sub>G</sub> is equal to the voltage across divider resistor **R**<sub>2</sub>:

$$\mathbf{V}_{\mathrm{G}} = \frac{\mathbf{R}_{2}\mathbf{V}_{\mathrm{DD}}}{\mathbf{R}_{1} + \mathbf{R}_{2}}$$

**Using Kirchhoff's Law:**

$$\mathbf{V}_{\mathbf{GS}} = \mathbf{V}_{\mathbf{G}} - \mathbf{I}_{\mathbf{D}}\mathbf{R}_{\mathbf{S}}$$

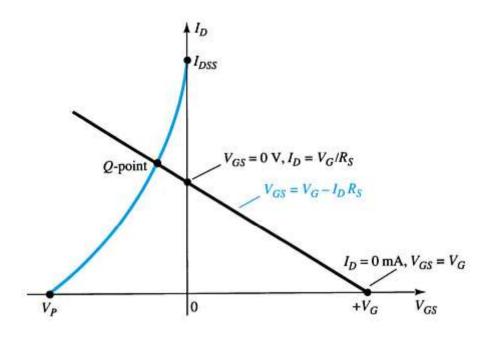

The Q point is established by plotting a line that intersects the transfer curve.

## Voltage-Divider Q-point

#### Step 1

Plot the line by plotting two points: • $V_{GS} = V_G$ ,  $I_D = 0 A$ • $V_{GS} = 0 V$ ,  $I_D = V_G / R_S$

#### Step 2

Plot the transfer curve by plotting  $I_{DSS},\,V_P$  and the calculated values of  $I_D$

#### Step 3

The Q-point is located where the line intersects the transfer curve

## **Voltage-Divider Bias Calculations**

Using the value of  $I_D$  at the Q-point, solve for the other variables in the voltage-divider bias circuit:

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

$$V_D = V_{DD} - I_D R_D$$

$$V_S = I_D R_S$$

$$I_{R1} = I_{R2} = \frac{V_{DD}}{R_1 + R_2}$$

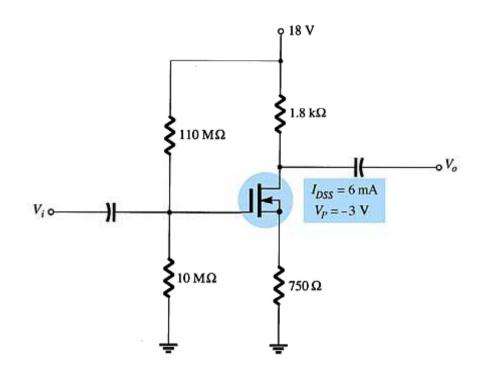

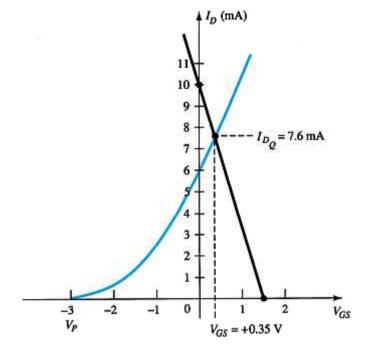

## **D-Type MOSFET Bias Circuits**

Depletion-type MOSFET bias circuits are similar to those used to bias JFETs. The only difference is that depletion-type MOSFETs can operate with positive values of  $V_{GS}$  and with  $I_D$  values that exceed  $I_{DSS}$ .

### **Self-Bias**

#### Step 1

Plot line for  $V_{GS} = V_G, I_D = 0 A$  $V_D = V_G/R_S, V_{GS} = 0 V$

#### Step 2

Plot the transfer curve using  $I_{\text{DSS}},\,V_{\text{P}}$  and calculated values of  $I_{\text{D}}$

#### Step 3

The Q-point is located where the line intersects the transfer curve. Use the  $I_D$  at the Q-point to solve for the other variables in the voltage-divider bias circuit.

These are the same steps used to analyze JFET self-bias circuits.

## **Voltage-Divider Bias**

#### Step 1

#### Plot the line for $V_{GS} = V_G, I_D = 0 A$ $V_D = V_G/R_S, V_{GS} = 0 V$

#### Step 2

Plot the transfer curve using  $I_{DSS}$ ,  $V_P$  and calculated values of  $I_D$ .

#### Step 3

The Q-point is located where the line intersects the transfer curve is. Use the  $I_D$  at the Q-point to solve for the other variables in the voltage-divider bias circuit.

## These are the same steps used to analyze JFET voltage-divider bias circuits.

## **E-Type MOSFET Bias Circuits**

The transfer characteristic for the e-type MOSFET is very different from that of a simple JFET or the d-type MOSFET.

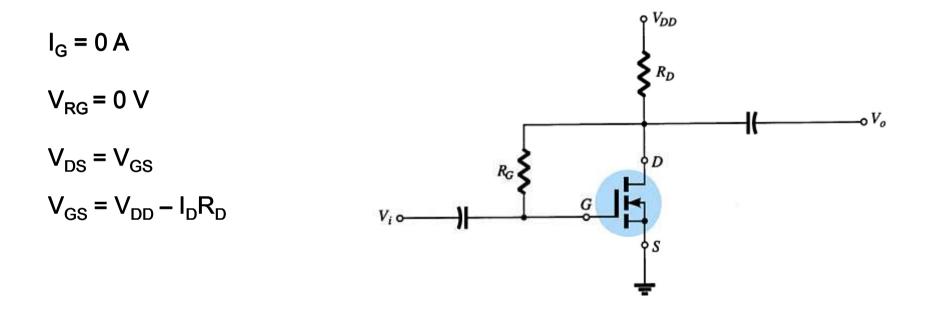

## **Feedback Bias Circuit**

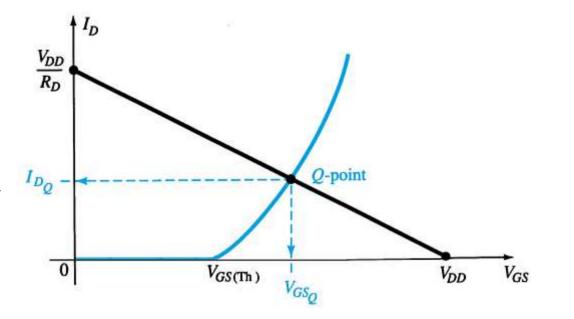

## **Feedback Bias Q-Point**

#### Step 1 Plot the line using $\cdot V_{GS} = V_{DD}, I_D = 0 A$ $\cdot I_D = V_{DD} / R_D, V_{GS} = 0 V$

#### Step 2

Using values from the specification sheet, plot the transfer curve with

•

$$V_{GSTh}$$

,  $I_D = 0 A$

• $V_{GS(on)}$ ,  $I_{D(on)}$

#### Step 3

The Q-point is located where the line and the transfer curve intersect

#### Step 4

Using the value of  $I_D$  at the Q-point, solve for the other variables in the bias circuit

## **Voltage-Divider Biasing**

Plot the line and the transfer curve to find the Q-point. Use these equations:

$$V_{G} = \frac{R_{2}V_{DD}}{R_{1} + R_{2}}$$

$$V_{GS} = V_{G} - I_{D}R_{S}$$

$$V_{DS} = V_{DD} - I_{D}(R_{S} + R_{D})$$

## Voltage-Divider Bias Q-Point

#### Step 1

Plot the line using

$$V_{GS} = V_G = (R_2 V_{DD}) / (R_1 + R_2), I_D = 0 A$$

$V_D = V_G / R_S, V_{GS} = 0 V$

#### Step 2

Using values from the specification sheet, plot the transfer curve with

• $V_{GSTh}$ ,  $I_D = 0 A$ • $V_{GS(on)}$  ,  $I_{D(on)}$

#### Step 3

The point where the line and the transfer curve intersect is the Q-point.

#### Step 4

Using the value of  $I_D$  at the Q-point, solve for the other circuit values.

For *p*-channel FETs the same calculations and graphs are used, except that the voltage polarities and current directions are reversed.

The graphs are mirror images of the *n*-channel graphs.

## **Applications**

Voltage-controlled resistor JFET voltmeter Timer network Fiber optic circuitry MOSFET relay driver