#### **ARM** Processors

-Swarna Prabha Jena Department of ECE

## **ARM Powered Products**

2

#### File File Incomentation File File File

. . . . . . . . . . . . . . . .

## The History of ARM

- Developed at Acorn Computers Limited, of Cambridge, England, between 1983 and 1985

- Problems with CISC:

- Slower then memory parts

- Clock cycles per instruction

## The History of ARM (2)

- Solution the Berkeley RISC I:

- Competitive

- Easy to develop (less than a year)

- Cheap

- Pointing the way to the future

#### Why learn ARM?

5

•!• Dominant architecture for embedded systems

•!•32 bits=> powerful & fast

•• Efficient: very low power/MI PS

•!•Regular instruction set with many advanced features.

#### Beyond MUO - A first look at ARM

- Complete instruction set.

- Larger address

- Subroutine call mechanism

- Additional internal registers

- Interrupts, direct memory access (DMA), and cache memory.

Interrupts: allow external devices (e.g. mouse, keyboard) to interrupt the current program execution

- •!• DMA: allows external high• throughput devices (e.g. display card) to access memory directly rather than through processor

- •!• Cache: a small amount of fast memory on the processor

#### The ARM Instruction Set

- Load-Store architecture

- Fixed-length (32-bit) instructions

- 3-operand instruction format (2 source operand regs, 1 result operand reg): ALU operations very powerful (can include shifts)

- Conditional execution of ALL instructions (v. clever idea!)

- Load-Store multiple registers in one instruction

- A single-cycle n-bit shift with ALU operation

- "Combines the best of RISC with the best of CISC"

## **Operating Modes**

#### User mode

- Normal program execution mode

- System resources unavailable

- Mode can be changed by supervisor only

#### **Supervisor modes**

- Entered upon exception

- Full access

to system resources

- Mode changed freely

#### **ARM Programmer's Model**

rO

1

r2

r3

r4

r5

r6

r7

r8

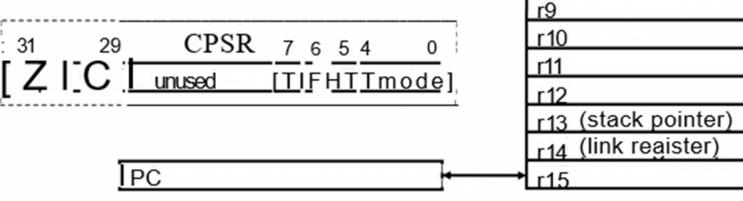

- 16 X 32 bit registers

- R15 is equal to the PC

- Its value is the current PC value

- Writin g to it causes a branch!

- RO-R14 are general purpose

- R13, R14 have additional functions, described later

- Current P rocessor Status Register (CPSR)

- Holds condition codes i.e status bits

**ARM Visible Registers**

## **ARM Programmer's Model**

$\left| \left( \right) \right|$

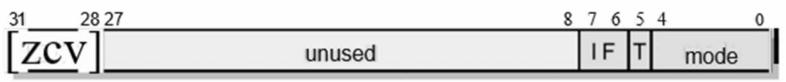

- CPSR is a special register, it cannot be read or written like other registers

- The result of any data processing instruction can modify status bits (flags)

- •!• These flags are read to determine branch conditions etc

#### Main status bits (condition codes):

- N (result was negative)

- Z (result was zero)

- •!• C (result involved a carry-out)

- · V (result overflowed as signed number)

- Other fields described later

#### ARM CPSR format

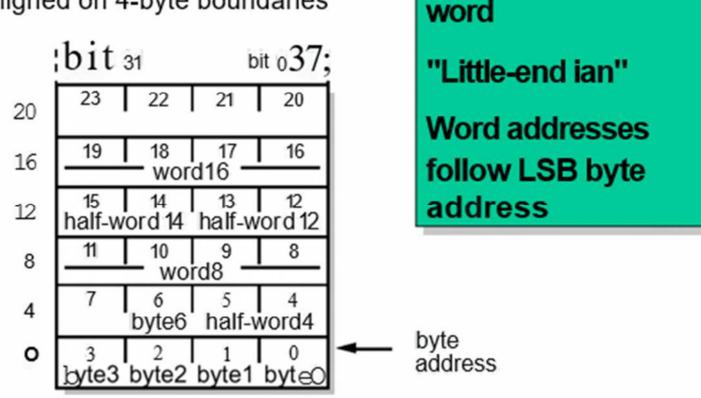

#### **ARM's memory organization**

11

NB - Lowest byte

address = LSB of

- Byte addressed memory

- Maximum 2<sup>32</sup> bytes of memory

- A word = 32-bits, half-word = 16 bits

- Words aligned on 4-byte boundaries

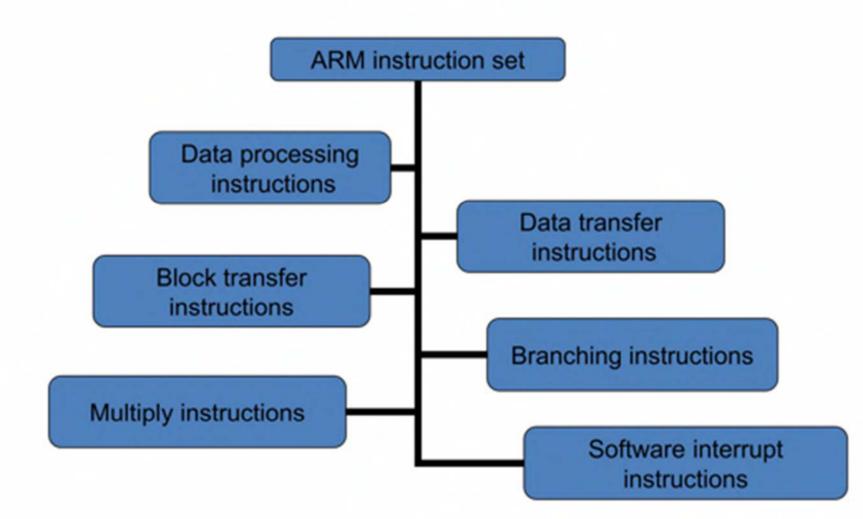

## ARM Instruction Set (3)

## **Data Processing Instructions**

- Arithmetic and logical operations

- 3-address format:

- Two 32-bit operands

- (opl is register, op2 is register or immediate)

- 32-bit result placed in a register

- Barrel shifter for op2 allows full 32-bit shift within instruction cycle

## Data Processing Instructions (2)

- Arithmetic operations:

- ADD, ADDC, SUB, SUBC, RSB, RSC

- Bit-wise logical operations:

- AND, EOR, ORR, BIC

- Register movement operations:

- MOV, MVN

- Comparison operations:

- TST, TEQ, CM P, CM N

Powerful tools for efficient coded programs

## Data Processing Instructions (4)

Example

if (z==1)

R1=R2+(R34)

compiles to

EQADDS R1,R2,R3, LSL #2

(SINGLE INSTRUCTION !)

## **Data Transfer Instructions**

- Load/store instructions

- Used to move signed and unsigned

Word, Half Word and Byte to and from registers

- Can be used to load PC (if target address is beyond branch instruction range)

| LDR   | Load Word             | STR   | Store Word             |

|-------|-----------------------|-------|------------------------|

| LDRH  | Load Half Word        | STRH  | Store Half Word        |

| LDRSH | Load Signed Half Word | STRSH | Store Signed Half Word |

| LDRB  | Load Byte             | STRB  | Store Byte             |

| LDRSB | Load Signed Byte      | STRSB | Store Signed Byte      |

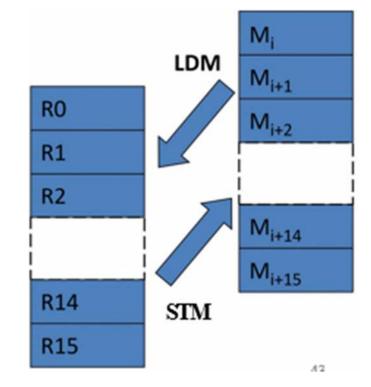

## **Block Transfer Instructions**

- Load/Store Multiple instructions (LDM/STM)

- Whole register bank or a subset copied to memory or restored with single instruction

## **Swap Instruction**

- Exchanges a word between registers

- Two cycles but

- single atomic action

- Support for RT semaphores

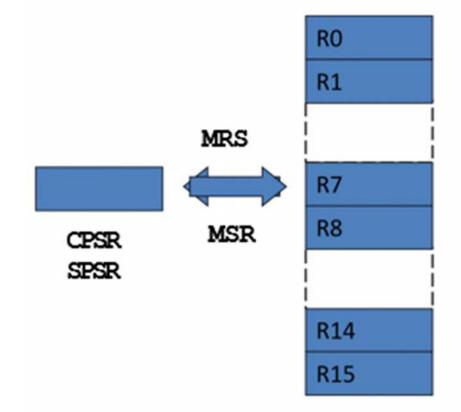

# Modifying the Status Register 20

- Only indirectly

- MSR moves contents fram CPSR/SPSR to selected GPR

- MRS moves contents from selected GPR to CPSR/SPSR

- Only in privileged modes

# Multiply Instructions 21

- Integer multiplication (32-bit result)

- Long integer multiplication (64-bit result)

- Built in Multiply Accumulate Unit (MAC)

- Multiply and accumulate instructions add product to running total

## **Multiply Instructions**

• Instructions:

| MUL    | Multiply                     | 32-bit result |

|--------|------------------------------|---------------|

| MULA   | Multiply accumulate          | 32-bit result |

| UMULL  | Unsigned multiply            | 64-bit result |

| UMLAL  | Unsigned multiply accumulate | 64-bit result |

| SMULL  | Signed multiply              | 64-bit result |

| SMILAL | Signed multiply accumulate   | 64-bit result |

# **Branching Instructions**

23

- Branch (B): jumps forwards/backwards up to 32 MB

- Branch link (BL):

same+ saves (PC+4) in LR

- Suitable for function call/return

- Condition codes for conditional branches

# **Branching Instructions (2)**

- Branch exchange (BX) and Branch link exchange (BLX): same as B/BL + exchange instruction set (ARM ++THUMB)

- Only way to swap sets

## **Thumb Instruction Set**

- Compressed form of ARM

- Instructions stored as 16-bit,

- Decompressed into ARM instructions and

- Executed

- Lower performance (ARM 40% faster)

- Higher density (THUM B saves 30% space)

- Optimal -

*"interworking"* (combining two sets) - compiler supported

# **THUMB Instruction Set (2)**

- More traditional:

- No condition codes

- Two-address data processing instructions

- Access to RO R8 restricted to

- MOV, ADD, CMP

- PUSH/POP for stack manipulation

- Descending stack (SP hardwired to R13)

- No MSR and MRS, must change to ARM to modify CPSR (change using BX or BLX)

- ARM entered automatically after RESET or entering exception mode

- Maximum 255 SWI calls

#### **ARM Assembly Quick Recap**

| MOV ra, rb<br>MOV ra, #n                                                        | ra := rb<br>ra := n                                                                             | n decimal in range -128 to 127<br>(other values possible, see later)                                                                                                                  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD ra, rb, re<br>ADD ra, rb, #n                                                | ra := rb + re<br>ra := rb + n                                                                   | ◆SUB => - instead of+                                                                                                                                                                 |

| CMP ra, rb<br>CMP ra, #n                                                        | set status bits on ra-rb<br>set status bits on ra-n                                             | •CMP is like SUB but has no destination register ans sets status bits                                                                                                                 |

| B label                                                                         | branch to label                                                                                 | BL label is branch & link                                                                                                                                                             |

| BEQ label<br>BNE label<br>BMI label<br>BPL label                                | branch to label if zero<br>branch if not zero<br>branch if negative<br>branch if zero or plus   | Branch conditions apply to the result of the last instruction to set status bits (ADDS/SUBS/MOVS/CMP etc).                                                                            |

| LDR ra, label<br>STR ra, label<br>ADR ra, label<br>LDR ra, [rb]<br>STR ra, [rb] | ra := mem[label]<br>mem[label] := ra<br>ra :=address of label<br>ra := mem[rb]<br>mem[rb] := ra | <pre> LDRB/STRB =&gt; byte transfer  Other address modes: [rb,#n] =&gt; mem[rb+n] [rb,#n]! =&gt; mem[rb+n], rb := rb+n [rb],#n =&gt; mem[rb], rb:=rb+n [rb+ri] =&gt; mem[rb+ri]</pre> |